In context: NVMe is a set of specifications that define a high-performance storage access protocol, allowing fast data transfers directly between CPUs and non-volatile storage media over the PCIe bus. UCIe, meanwhile, is a separate standard that aims to establish an open interface for integrating modular chiplets into package systems, enabling a more flexible and scalable approach to chip design. Both of these cutting-edge technologies just leveled up with major specification releases.

The NVMe technology update includes three brand new specifications: the NVMe Boot specification, the Subsystem Local Memory command set, and the Computational Programs command set. The consortium said these specifications aim to facilitate “faster and simpler development” of the architecture.

They also updated eight existing specs covering the base NVMe command set, transports like PCIe and Fibre Channel, NVMe management, and more.

The new and revised standards pack affords some seriously cool capabilities. We’re talking live migration of NVMe controllers between subsystems, host-directed data placement for easier SSD integration, support for offloading some host processing to storage, network boot support, NVMe over Fabrics zoning, and better encryption management, just to name a few.

As Peter Onufryk, the NVM Express Technical Workgroup Chair puts it, “NVMe technology has grown into nearly a dozen specifications, including multiple command sets, that provide pivotal support for NVMe technology across all major transports and standardize many aspects of storage.”

He added that with 75 new authorized technical proposals already in the works, the future of NVMe is looking bright for unified client, cloud, AI, and enterprise architectures.

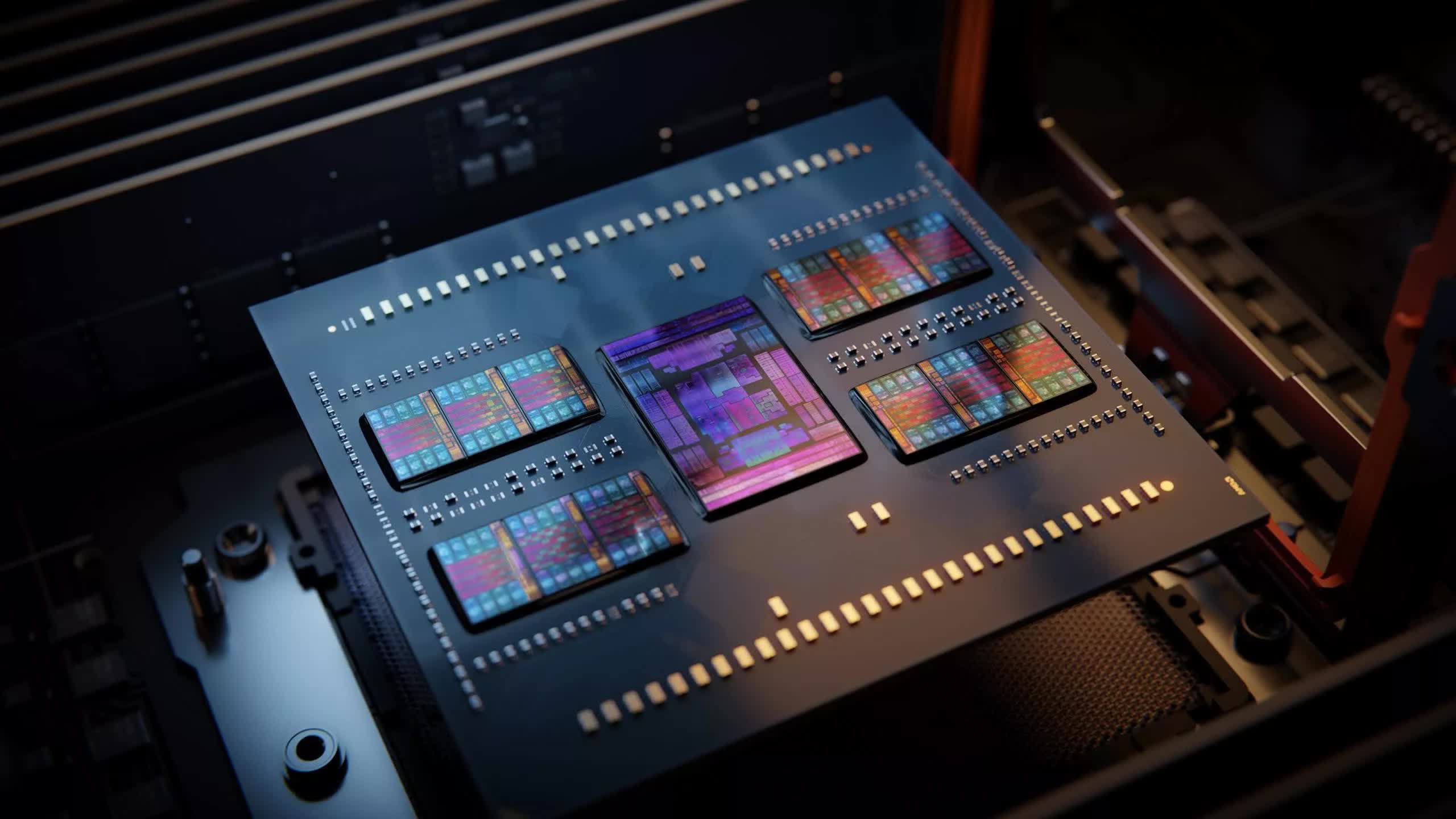

Not to be outdone, the UCIe Consortium also delivered with their 2.0 spec release. A key focus is improving manageability and testing for multi-chip system-in-package (SIP) designs. UCIe 2.0 adds an optional “DFx Architecture” that essentially bakes management fabric into each chiplet. This control plane allows vendor-agnostic testing, telemetry, and debugging across the whole SIP lifecycle.

Official 3D packaging support has also arrived. UCIe-3D promises way higher bandwidth density and better power efficiency versus 2D or 2.5D chiplet layouts. It uses advanced hybrid bonding with insanely tight bump pitches down to 1 micron or below.

As for testing, the new release establishes a compliance program to validate UCIe implementations against a reference design. There are defined physical, protocol, and adapter test specs to ensure interoperability between vendors. Other novelties include pre-optimized package blueprints and full backward compatibility with UCIe 1.0 and 1.1.

“The UCIe 2.0 Specification builds on previous iterations by developing a comprehensive solution stack and encouraging interoperability between chiplet solutions. This is yet another example of the Consortium’s dedication to the flourishing open chiplet ecosystem,” said UCIe president Cheolmin Park.